## CPE/EE 422/522 Advanced Logic Design L08

Electrical and Computer Engineering University of Alabama in Huntsville

## **Outline**

- · What we know

- How to model Combinational Networks in VHDL

- Structural, Dataflow, Behavioral

- How to model Flipflops in VHDL

- Processes

- Delays (delta, transport, inertial)

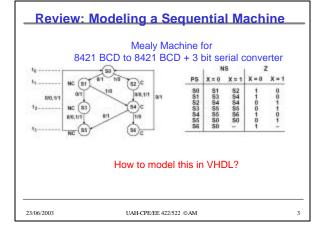

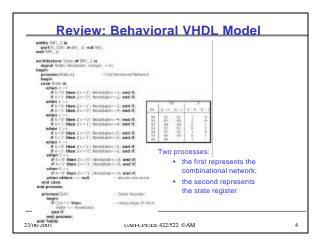

- How to model FSM in VHDL

- Wait statements

- Variables, Signals, Arrays

- · What we do not know

- VHDL Operators

- Procedures, Functions

- Packages, Libraries

- Additional Topics (if time)

6/2003 U

## **Review: Wait Statements**

- ... an alternative to a sensitivity list

- Note: a process cannot have both wait statement(s) and a sensitivity list

- Generic form of a process with wait statement(s)

```

process

begin

sequential-statements

wait statement

sequential-statements

wait-statement

...

end process;

```

How wait statements work?

• Execute seg. statement until

- a wait statement is encountered.

- Wait until the specified condition is satisfied.

- Then execute the next

- set of sequential statements until the next wait statement is encountered.

- When the end of the process is reached start over again at the beginning.

23/06/2003 UAH-CPE/EE 422/522 ©AM

## **Review: Forms of Wait Statements**

wait on sensitivity-list;

wait for time-expression;

wait until boolean-expression;

- · Wait on

- until one of the signals in the sensitivity list changes

- Wait for

- waits until the time specified by the time expression has elapsed

- What is this: wait for 0 ns;

- Wait until

- the boolean expression is evaluated whenever one of the signals in the expression changes, and the process continues execution when the expression evaluates to TRUE

23/06/2003

AH-CPE/EE 422/522 @ AM

## Review: Variables

- What are they for: Local storage in processes, procedures, and functions

- · Declaring variables

```

variable list_of_variable_names : type_name

[ := initial value ];

```

- Variables must be declared within the process in which they are used and are local to the process

- Note: exception to this is SHARED variables

23/06/2003 UAH-CPE/EE 422/522 ©AM 7

## Review: Signals

- Signals must be declared outside a process

- Declaration form

```

signal list_of_signal_names : type_name

[ := initial value ];

```

• Declared in an architecture can be used anywhere within that architecture

23/06/2003

UAH-CPE/EE 422/522 © AM

## **Review: Constants**

Declaration form

```

constant constant_name : type_name := constant_value;

constant delay1 : time := 5 ns;

```

- Constants declared at the start of an architecture can be used anywhere within that architecture

- Constants declared within a process are local to that process

23/06/2003 UAH-CPE/EE 422/522 ©AM

## **Review: Variables vs. Signals**

Variable assignment statement

variable\_name := expression;

- expression is evaluated and the variable is instantaneously updated (no delay, not even delta delay)

- Signal assignment statement

```

signal_name <= expression [after delay];

```

expression is evaluated and the signal is scheduled to change after delay; if no delay is specified the signal is scheduled to be updated after a delta delay

23/06/2003 UAH-CPE/EE 422/522 @AM

## Review: Variables vs. Signals (cont'd)

## Process Using Variables entity durning is entity

UAH-CPE/EE 422/522 ©AM

23/06/2003

## Predefined VHDL Types

- Variables, signals, and constants can have any one of the predefined VHDL types or they can have a user-defined type

- Predefined Types

- $\ bit \{ \text{`0'}, \, \text{`1'} \}$

11

- boolean {TRUE, FALSE}

- integer  $-[-2^{31} 1.. 2^{31} 1]$

- real floating point number in range -1.0E38 to +1.0E38

- character legal VHDL characters including loweruppercase letters, digits, special characters, ...

- time an integer with units fs, ps, ns, us, ms, sec, min, or hr

23/06/2003 UAH-CPE/EE 422/522 ©AM 12

## **User Defined Type**

• Common user-defined type is enumerated

```

type state_type is (S0, S1, S2, S3, S4, S5);

signal state : state_type := S1;

```

- If no initialization, the default initialization is the leftmost element in the enumeration list (S0 in this example)

- VHDL is strongly typed language => signals and variables of different types cannot be mixed in the same assignment statement, and no automatic type conversion is performed

23/06/2003 UAH-CPE/EE 422/522 @AM

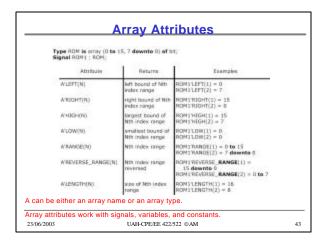

## **Arrays**

• Example

```

type SHORT_WORD is array (15 downto 0) of bit;

signal DATA_WORD : SHORT_WORD;

variable ALT_WORD : SHORT_WORD := "01010101010101010101";

constant ONE_WORD : SHORT_WORD := (others => '1');

```

- ALT\_WORD(0) rightmost bit

- ALT\_WORD(5 downto 0) low order 6 bits

- · General form

## Arrays (cont'd)

Multidimensional arrays

```

type matrix4x3 is array (1 to 4, 1 to 3) of integer;

variable matrixA: matrix4x3 :=

((1,2,3), (4,5,6), (7,8,9), (10,11,12));

```

- matrixA(3, 2) = ?

- · Unconstrained array type

type intvec is array (natural range<>) of integer;

type matrix is array (natural range<>, natural range<>)

of integer;

· range must be specified when the array object is declared

**signal** intvec5 : intvec(1 to 5) := (3,2,6,8,1);

23/06/2003 UAH-CPE/EE 422/522 ©AM 15

## **Predefined Unconstrained Array Types**

· Bit\_vector, string

type bit\_vector is array (natural range <>) of bit; type string is array (positive range <>) of character; constant string1: string(1 to 29) := "This string is 29 characters."

constant A : bit\_vector(0 to 5) := "10101"; -- (`1', `0', `1', `0', `1');

- Subtypes

- include a subset of the values specified by the type

- subtype SHORT\_WORD is : bit\_vector(15 to 0);

- · Predefined subtypes of type integer

- POSITIVE (all positive integers)

- NATURAL (all positive integers and 0)

UAH-CPE/EE 422/522 @AM

## **VHDL Operators**

- 1. Binary logical operators: and or nand nor xor xnor

- 2. Relational: = /= < <= > >=

- 3. Shift: sll srl sla sra rol ror

- 4. Adding: + & (concatenation)

- 5. Unary sign: + -

- 6. Multiplying: \* / mod rem

- 7. Miscellaneous: not abs \*\*

- Class 7 has the highest precedence (applied first), followed by class 6, then class 5, etc

23/06/2003 UAH-CPE/EE 422/522 @AM

## **Example of VHDL Operators**

In the following expression, A, B, C, and D are bit\_vectors:

(A & not B or C ror 2 and D) = "110010"

The operators would be applied in the order:

not, 8, ror, or, and, -

Jf. A = "110", B = "111", C = "011000", and D = "111011", the computation would proceed as

not B = "000" (bit-by-bit complement)

A 5. mot B = "110000" (concatenation) C ror 2 = "000110" (rotate right 2 places)

(A & not B) or (C ror 2) = "110110" (bit-by-bit or)

(A & not 8 or C ror 2) and D = "110010" (bit-by-bit and)

[(A & not 8 or C ror 2 and D) = "110010"] = TRUE

(the parentheses force the equality test to be done last and the result is TRUE)

23/06/2003

UAH-CPE/EE 422/522 ©AM

## **Example of Shift Operators**

The shift operators can be applied to any bit\_vector or boolean\_vector. In the following examples, A is a bit\_vector equal to "10010101":

A sill 2 is "01010100" (shift left logical, filled with '0')

A srl 3 is "00010010" (shift right logical, filled with '0')

A sia 3 is "10101111" (shift left arithmetic, filled with right bit)

A sra 2 is "11100101" (shift right arithmetic, filled with left bit)

A rol 3 is "10101100" (rotate left)

A ror 5 is "10101100" (rotate right)

23/06/2003

19

UAH-CPE/EE 422/522 ©AM

•5

## **VHDL Functions**

· Functions execute a sequential algorithm and return a single value to calling program

```

function rotate_right (reg: bit_vector)

return bit_vector is

begin

return reg ror 1;

end rotate_right;

```

• A = "10010101"

B <= rotate right(A);

· General form

function function-name (formal-parameter-list)

return return-type is [declarations] begin

sequential statements -- must include return return-value; end function-name;

21 23/06/2003

## **For Loops**

```

General form of a for loop:

```

[loop-label:] for loop-index in range loop

sequential statements end loop [loop-label];

Exit statement has the form:

22

exit when condition;

## For Loop Example:

compare two 8-character strings and return TRUE if equal function comp\_string(string1, string2: string(1 to 8)) return boolean is

variable B: boolean:

begin loopex: for j in 1 to 8 loop

B := string1(j) = string2(j); exit when B=FALSE; end loop loopex;

return B; end comp\_string;

## **Add Function**

```

-- This function adds 2.4-bit vectors and a carry,

```

-- It returns a 5-bit sum

function add4 (A,B: bit\_vector(3 downto 0); carry: bit) return bit\_vector is

variable cost: bit; variable cin: bit := carry; variable Sum: bit\_vector(4 downto 0):="00000";

begin

begin loop1: for i in 0 to 3 loop court := (A(i) and B(i)} or (A(i) and C(i)] or (B(i) and C(i); som (i) := A(i) xor B(i) xor C(i); this := C(i) xor C(i); this := C(i) xor C(i) x

end loop loop1;

Sum(4):= cout; return Sum; end add4;

Example function call:

Sum1 <- add4(A1, B1, cin);

23/06/2003 UAH-CPE/EE 422/522 ©AM

## **VHDL Procedures**

- · Facilitate decomposition of VHDL code into modules

- Procedures can return any number of values using output parameters

- General form

```

procedure procedure_name (formal-parameter-list) is

[declarations]

```

begin

Sequential-statements end procedure\_name;

procedure\_name (actual-parameter-list);

23/06/2003

23

UAH-CPE/EE 422/522 ©AM

## Procedure for Adding Bit\_vectors -- This procedure adds two n-bit bit\_vectors and a carry and -- returns an n-bit sum and a carry. Add1 and Add2 are assumed -- to be of the same length and dimensioned n-1 downto 0. procedure Addvec [Add1, Add2: in bit\_vector; Cin: in bit. signal Sum: out bit\_vector; signal Cust; out bit; n:in posthre) is variable C: bit; begin C:= Cin; for i in 0 to n-1 loop Sum():= Add1(i) and Add2(i) or (Add1(i) and C) or (Add2(i) and C); end loop; Cust <= C; end Addvec; Example procedure call: Addvec(A1, B1, Cin, Sum1, Cost, 4); 2306/2003 UAH-CPE/EE 422/522 ©AM 25

## **Packages and Libraries**

- Provide a convenient way of referencing frequently used functions and components

- · Package declaration

package package-name is package declarations end [package][package-name];

· Package body [optional]

package body package-name is package body dedarations end [package body][package name];

23/06/2003 UAH-CPE/EE 422/522 ©AM 27

## package 16\_pack is medical and instruction of the pack package component over present of the package of the package of the package is package in the package of the package of the package of the package is package of the package o

## pechage body IIC\_200.18 — This flantion eith 2.4-bit mindows, informs a 5-bit sem flantides acide (rogs, tapp) bit, vector() deserted (typer); bit) seminors acided (rogs, tapp) bit, vector() deserted (typer); bit) seminors acided (rogs, tapp) bit, vector() deserted (typer); bit) seminors acided (rogs, tapp) control (rogs) (rogs, tapp) control (rogs,

```

Library BITLIB — bit_pack package

Components in Library BIFLIB includes

—3 input AND gase

exitity And its

general (DELAN terral)

pert (AL, PA, Abt. in bit; 2: out bit;)

meditecture concur of And in

bigs;

and included and and As affect DELAY;

medit.

— D Right Plas

metity Off in

general (DELAN terral)

general (DELAN terr

```

## VHDL Model for a 74163 Counter

- 74613 4-bit fully synchronous binary counter

- Counter operations

| Control Signals |     |     | Next State        |     |     |                   |                 |

|-----------------|-----|-----|-------------------|-----|-----|-------------------|-----------------|

| ClrN            | LdN | P+T | Q3*               | QZ* | Q1* | Q0*               |                 |

| .0              | ×   | X   | 0                 | 0   | 0   | 0                 | (clear)         |

| 1               | .0  | X   | D3                | D/2 | D1  | DO:               | (parallel load) |

| 1               | 1   | 0   | Q3                | Q2  | Q1  | Q0                | (no change)     |

| 1               | 1   | 1   | present state + 1 |     |     | (increment count) |                 |

- Generate a Cout in state 15 if T=1

- Cout =  $Q_3Q_2Q_1Q_0T$

23/06/2003 UAH-CPE/EE 422/522 ©AM 31

## **Additional Topics in VHDL**

- Attributes

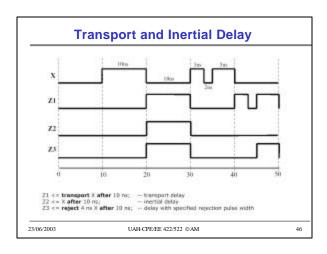

- Transport and Inertial Delays

- Operator Overloading

- Multivalued Logic and Signal Resolution

- IEEE 1164 Standard Logic

- Generics

- · Generate Statements

- · Synthesis of VHDL Code

- · Synthesis Examples

- Files and Text IO

23/06/2003 UAH-CPE/EE 422/522 ©AM 35

## Signal Attributes Attributes associated with signals that return a value Returns True if an event occurred during the current deta, else false STVENT True if a transaction occurred during the ourrent delta, else false S'ACTIVE STAST EVENT Time elassed since the previous event on S. S'LAST VALUE Value of S before the previous event on S STAST\_ACTIVE Time elapsed since previous transaction on S A'event - true if a change in S has just occurred A'active - true if A has just been reevaluated, even if A does not change 23/06/2003 UAH-CPE/EE 422/522 ©AM 36

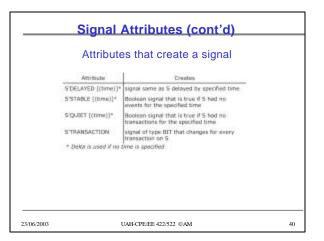

## Signal Attributes (cont'd)

- Event

- occurs on a signal every time it is changed

- Transaction

- occurs on a signal every time it is evaluated

- Example:

```

A <= B - - B changes at time T

```

|        | A'event | B'event |

|--------|---------|---------|

| т      |         |         |

| T + 1d |         |         |

23/06/2003 UAH-CPE/EE 422/522 ©AM 3

## Signal Attributes (cont'd) entity test is if (A'event) then Aev := '1'; else Aev := '0'; architecture bmtest of test is end if; if (A'active) then Aac := '1'; else Aac := '0'; signal A : bit; signal B : bit; end if; signal C : bit; if (B'event) then Bev := '1'; else Bev := '0'; A <= not A after 20 ns; end if; B <= '1'; else Bac := '0'; end if; $C \le A$ and B;process(A, B, C) variable Aev : bit; if (C'event) then Cev := '1'; else Cev := '0'; variable Aac : bit; end if; if (C'active) then Cac := '1'; variable Bev : bit; variable Bac : bit; else Cac := '0'; end if; variable Cev : bit; variable Cac : bit; end process; UAH-CPE/EE 422/522 © AM 23/06/2003 38

## Signal Attributes (cont'd) /test/a /test/line\_\_15/bev delta /test/b /test/line\_\_15/bac /test/c /test/line\_\_15/cev /test/line\_\_15/aev /test/line\_\_15/cac /test/line\_\_15/aac 0 +0 0 0 0 0 0 0 0 0 0 0 +1 0 1 0 0 0 1 1 0 1 0 0 0 0 1 1 0 1 1 20 +0 20 +1 1 1 1 0 0 0 1 1 1 1 0 0 1 1 40 +0 0 0 0 0 40 +1 0 0 1 1 0 1 0 0 0 23/06/2003 UAH-CPE/EE 422/522 ©AM 39

```

Recap: Adding Vectors

- This procedure adds two n-bit bit, vectors and a carry and

- returns an n-bit sum and a carry. Add I and Add2 are essumed

- to be of the sums bright and dimensioned s-1 downto 0.

procedure Addec(

(Add1, Add2: in bit, vector)

(Signal Sum: out bit, vector)

signal Sum: out bit, vector)

sign

```

## Procedure for Adding Bit Vectors - This procedure adds the bit\_vectors and a carry and returns a sum and a carry. Both bit\_vectors should be of the same length. procedure Addive? (Addit\_AddIt in bit\_vector): (Cor: In bit; signal Sum: out bit\_vector): (signal Cout: out bit) is variable C bit ! = Chit; alias n1: bit\_vector[AddIt ength-1 downbo 0] is Add1; alias n1: bit\_vector[AddIt ength-1 downbo 0] is Add1; alias s1: bit\_vector[Sum/kength-1 downbo 0] is Add2; alias S: bit\_vector[Sum/kength-1 downbo 0] is Add1; begin assert ((n1)kength = n2/kength) and (n1 length = Slength)) report "vector lengths must be opad!" severity error; for i in s'recorse, range loop S(i) = n1(0) xon n1(i) xor C; C := (n1(i) and n2(i)) or (n1(i) and C) or (n2(i) and C); end Addres2; 23/06/2003 UAH-CPE/EE 422/522 @AM 45

## Transport and Inertial Delay (cont'd) Z3 <= reject 4 ns X after 10 ns; Reject is equivalent to a combination of inertial and transport delay: Zm <= X after 4 ns; Z3 <= transport Zm after 6 ns; Statements executed at time T - B at T+1, C at T+2 A <= transport B after 1 ns; A <= transport C after 2 ns; Statements executed at time T Statements executed at time T -C at T + 1: -C at T + 2 A <= B after 1 ns; A <= transport B after 2 ns; A <= C after 2 ns; A <= transport C after 1 ns; 23/06/2003 UAH-CPE/EE 422/522 @AM 47

## Operator Overloading

- Operators +, operate on integers

- Write procedures for bit vector addition/subtraction

addvec, subvec

- Operator overloading allows using + operator to implicitly call an appropriate addition function

- · How does it work?

- When compiler encounters a function declaration in which the function name is an operator enclosed in double quotes, the compiler treats the function as an operator overloading ("+")

- when a "+" operator is encountered, the compiler automatically checks the types of operands and calls appropriate functions

23/06/2003 UAH-CPE/EE 422/522 ©AM 48

##

UAH-CPE/EE 422/522 © AM

23/06/2003

## **Overloaded Operators**

- A, B, C bit vectors

- $A \le B + C + 3$ ?

- A <= 3 + B + C ?

49

- Overloading can also be applied to procedures and functions

- procedures have the same name –

type of the actual parameters in the procedure call determines which version of the procedure is called

23/06/2003 UAH-CPE/EE 422/522 ®AM 50

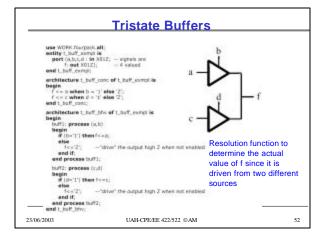

## Bit (0, 1) Tristate buffers and buses => high impedance state 'Z' Unknown state 'X' e. g., a gate is driven by 'Z', output is unknown a signal is simultaneously driven by '0' and '1' 23/06/2003 UAH-CPE/EE 422/522 @AM

Multivalued Logic

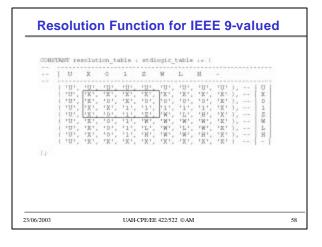

## **Signal Resolution**

- VHDL signals may either be resolved or unresolved

- Resolved signals have an associated resolution function

- · Bit type is unresolved -

- there is no resolution function

- if you drive a bit signal to two different values in two concurrent statements, the compiler will generate an error

23/06/2003 UAH-CPE/EE 422/522 @AM 53

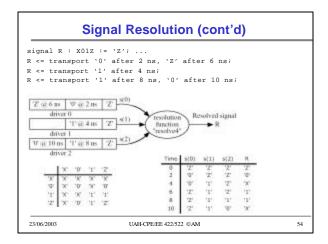

# package fluerpoix 8 \*\*Gyee a wide is (16,10,11,12); - u\_wide is attreashed type u\_wide is (16,10,11,12); - u\_wide is attreashed type u\_wide is (16,10,11,12); - u\_wide is attreashed type u\_wide is active u\_wide; u\_wide is u\_wide is u\_wide in u\_wide is u\_wide in u\_wi

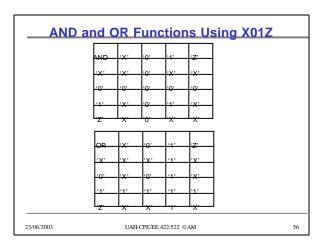

## **IEEE 1164 Standard Logic** • 9-valued logic system - 'U' - Uninitialized - 'X' - Forcing Unknown - '0' - Forcing 0 If forcing and weak signal are - '1' - Forcing 1 tied together, the forcing signal dominates. - 'Z' - High impedance - 'W' - Weak unknown Useful in modeling the internal - 'L' - Weak 0 operation of certain types of ICs. - 'H' - Weak 1 - '-' - Don't care In this course we use a subset of the IEEE values: X10Z UAH-CPE/EE 422/522 @AM 23/06/2003 57

```

AND Function for std_logic_vectors

function 'and' [1:std_ulogic; r:std_ulogic] return UNDL is begin return (and_table(), r)];

and 'and':

function 'and' [Uristd_logic_vector] return std_logic_vector is alias in std_logic_vector (i to INLEWGTH ) is r)

alias in std_logic_vector (i to INLEWGTH) is r)

variable result: std_logic_vector (i to FLEWGTH);

begin

if (INLEWGTH) = FLEWGTH) then

assert FALSE

report 'anguments of overloaded 'and' operator are not of the name length'

severity FALURE;

else

for in result RANGE loop

result() := and_table (Nr(I), re(I));

end loop,

end if;

return result;

end 'and';

23/06/2003

UAH-CPE/EE 422/522 ©AM 60

```